# 6GHzまで広がるCISPR 規制を視野に入れた高速・高周波電子回路 基板電源のRFブロック提案

A Proposal of R.F. Block to Work Power Rail at High-Frequency / High-Speed Circuits Board for CISPR Regulation Compliant up to 6GHz.

小 宮 邦文 Kunifumi Komiya

#### ケイアールエフエム株式会社 K.RF&MICROWAVE Corporation

**あらまし**: 電子回路部品の実装基板設計における、P I (Power Integrity)設計手段の主流である、キャパシタによる低インピーダンス化手法では、GHz帯域を超えてマイクロ波帯域まで広がる、広帯域ノイズの除去対策は難しい。 来年度から欧州と日本で規制運用が開始されるCISPR22対策にあたって、パッケージング(基板)設計者の多くが、問題を抱えている。 ここでは、その一つの解決手法について提案する。 この解法は、ショート(リング)回路を有する微少なコイルとキャパシタを用いたRFブロック(デカップリング)を、高速で動作するそれぞれの半導体のアイランド・セクション毎に搭載するというもので、広帯域のノイズ成分が阻止されることで、信号線路のSI(Signal Integrity)周波数特性改善も期待される。

The conventional method of Power Integrity in designing High-frequency / High-speed electronic systems by applying capacitors into power supply rail will not eliminate noises in higher frequency areas. Therefore, many system packaging designers face difficulties in developing systems. We KRFM would propose an useful method by an applying minute wounded coils with short-circuit rings into the power line associated with a cpacitor, causing eliminated high frequency noise level and improved performance.

キーワード: CISPR22規制、RFプロック、PI、SI、SSN

Keywords: CISPR22 reguration, R.F.Block, Power Integrity, Signal Integrity, Simultaneous Switching Noise

#### 1 まえがき

半導体デバイスの高速・高周波化にともなって、デバイスの集積度が飛躍的に高くなってきたことから、半導体集積回路に電源を供給する基板線路の電流変化量も増え続けて、CMOSトランジスタのスイッチング動作時に発生する、電源ノイズ(SSN)問題が、日を追う毎に顕在化してきた。

#### 2 電源線路等価回路 と ノイズ

半導体を実装(搭載)するパッケージやPCBの電源供給線路には、色々なパッシブ素子成分が寄生している。 それらを総合して、電源線路の等価回路と見なした時の、線路のインピーダンスを Z とすると、電源

(線路) ノイズは、この電源線路を流れる電流の変化量 *I*と、その電源線路のインピーダンス *Z*との積と定義される。

そして、この電源線路ノイズをコントロールするためには、電源線路のインピーダンス Z を下げるか、電流変化量 / を低減するしかない。

だが、高速動作をする半導体のスピードを下げたり、ゲート数を減らすような物理的な低減は本末転倒であることから、タイミング・シフトなどのソフトウェア的手段も用いられるが、基板設計時のP I シミュレーションは、インピーダンスをさげるために、基板の隠れた寄生インダクタンスを洗い出すことと、バイパス・キャパシタを用いる低インピーダンス化で進められてきた。[1]

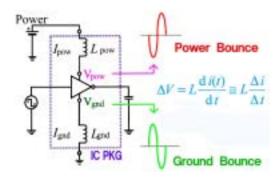

## 3 電源パウンス と グランド・パウンス

別の方向から電源に注目して見てみると、本来、電子回路設計時のグランド電位は0 ポルトを基準電位として設計されるが、半導体が搭載されている基板やパッケージには寄生のパッシブ素子成分があり、電源線路では、時間的に変化する電流によって下記のような電位変動が起こる。

$$\Delta V = \boldsymbol{I} \cdot \boldsymbol{R} + L \frac{\mathrm{d}i(t)}{\mathrm{d}t}$$

電源線路が空中に存在しているわけではないために寄生するパッシブ素子成分、特に線路の抵抗成分やインダクタンス成分によって引き起こされるグランド電位の変動は、「グランド・バウンス(Ground Bounce)」と呼ばれる。

勿論、電源はグランドだけではないので、これと同じ考えで、直流電源におけるプラス電位側でも電源電圧の変動は起こる。 こちらは「電源バウンス(Power Bounce)」といわれる。[2]

【図1】 電源バウンス と グラウンド・バウンス

これらの電源電圧変動も、半導体の動作速度が遅く、電流の変化時間も少ない場合には、問題はないが、クロック・スピードが高速になればなるほど、回路の動作に影響を与えるようになった。

そして、このグランド・バウンスや電源バウンスを低減する手法としては、基板側の電源線路やグランド線路の幅や厚みを増したり、半導体への電源端子を増やしたりといった、電源線路の寄生インダクタンスを下げる努力しか行われていない。

#### 4 電磁波ノイズ

電源供給線路網を「低インピーダンス線路」に換えるという、電流、電圧に着目した「Target Impedance Definition」によるPI (Power Integrity)シミュレーション設計手段を、多くの基板設計者は信奉してやってきたが、この手法を駆使して、うまくやればやるほど、その電源線路に、半導体集積回路から重畳(漏洩)してくる高周波電力(電磁波ノイズ)は、動作周波数が高周波化する一方で、阻止対策は後手に回っている。電磁波ノイズにとって、低インピーダンス線路は、絶好の伝搬線路である。

#### 5 CISPR22、32対策

来年度より運用が開始されるCISPR22規制や201 1年とも云われるCISPR32に対応できる電子回路機器を設計するためには、基板の電源線路に伝搬する高次調波を、6GHz以上にわたって阻止しなければならない。

けれども、マイクロ波帯域まで使用できるバイパス 用途のキャパシタが、見つからないこともあるが、果た して、キャパシタで電磁波ノイズは阻止できるのかとい う疑問がつきまとう。

マイクロ波帯の入り口まで広がった高次調波ノイズを、 部品メーカーが販売するチップ部品で対策するのは 難しいとも云われている。

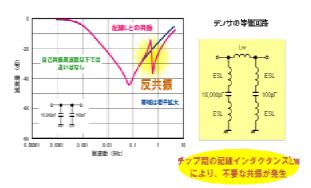

【図2】 異種のキャパシタによる反共振

集積された多量の半導体が、同時にスイッチングすることで、電源線路に高速な電流変化が起こって、電源線路に高周波/イスが発生する。

と考えるのか、はたまた、

高速で多量のスイッチングをしている半導体集積回 路自体から、低インピーダンスの電源に向かって高次 調波(エネルギー)が漏れ出て来て、電源線路に重畳 している。

と考えるのかは意見が分かれるころだが、いずれに しても、今までの Р I 手法では マイクロ波帯域まで広 がる電磁波(ノイズ)の電源線路への伝搬を食い止め ることはできない。

### ESR調整キャパシタ

電子部品実装基板上には、いろいろな材料の、構 造も異なる複数のキャパシタが搭載されている。それ はキャパシタでの「低インピーダンス化」帯域が比較的 狭い範囲しか実現しないために、いろいろな組み合わ せで広帯域に持って行こうとしている。

しかし、キャパシタの組み合わせによっては「反共 振」を起こしてしまうため、近年は等価直列抵抗(ES R)をある程度の値に調整したキャパシタが作られるよ うになった。

けれども、マイクロ波帯域までの広帯域にわたり「低 インピーダンス化」を実現できるキャパシタはない。

スイッチングする半導体自体が生成して、電源線路 に漏れて(伝わって)来る高次調波は、半導体チップ 内にあっては、方形(矩形)波が高速で立ち上がるた めに必要なエネルギー(高次調波成分)である。

しかし、電源線路とGNDの間にキャパシタを多 量に搭載する低インピーダンス化が実行されると、 キャパシタは電源線路側グランドに漏れてください とバイパスする訳だから、この方形(矩形)波に取っ て大事な高次調波エネルギーは高速性を維持する 能力を失ってしまう。

闇雲に色々な容量のキャパシタを半導体の電源端 子に搭載するのは、良くない。

### 7 相反するPIとEMC

あちらを立てれば、こちらが立たずとでも行ったら良 いのか、【表1】に示すように、PIを実現するための手 段としての「低インピーダンス化」は、EMC対策を実 現ための手段として、電源線路に要求する線路インピ ーダンスの要求とは、まるっきり逆で、高インピーダン スでなければ、電磁波(ノイズ)を阻止できない。

このような相反することを、基板設計で同時に実行 することは不可能であるが、「コイフィル」を使えばこの PIとEMCの問題は、解決する。

低い周波数においては、低インピーダンスで、GHz を超えるような高い周波数の電磁波(ノイズ)に対して は、高インピーダンスに見える個別部品、それが「コイ フィル」と呼ばれるコイル・インダクタです。

|                                 | P (<br>(Power Integrity)    | E M C (ElectroMagnetic<br>Compatibility) |

|---------------------------------|-----------------------------|------------------------------------------|

| Function                        | 電源電圧(電流変数)の影波               | 伝導(放射)電磁液の振鴻                             |

| 実現機能                            | 電源(グラウンF)パウンスの保護            | 電磁射性の強化                                  |

| Technique                       | 低インピーダンス化                   | チカップリング                                  |

| 実理手段                            | バスコン、シールド                   | バイバス、バイアス-T                              |

| Impedance                       | 製化/ピーダンス                    | 高インゼータンス                                 |

| インピーチンス                         | (高級のGrb帯 対策なし)              | (毎増は優インゼータンス)                            |

| Source of<br>Impossible<br>丰金要因 | 電源論論のパラシティック<br>同時スイッチングノイズ | コモン(ノーヤル)モード・ノイズ<br>結合共振、反共振、 罪契規表       |

【表1】相反するPIとEMCの対策

電子回路部品実装基板の設計の善し悪しが、電子 回路器機の動作に大きな影響を与えるようになっ てきた。

それと同時に、電源配線(プレーン)の急激な 電源変動による電磁波干渉 (Electro Magnetic Interference)が、ひいては電子回路器機(システム) の電磁環境適合性(Electro Magnetic Compatibility) 問題を起こすことにもつながる。

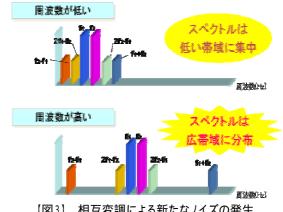

【図3】 相互変調による新たなノイズの発生

## 8 相互変調

2つの電磁波同士が干渉し合って、【図3】のように、本来は無いはずの周波数を、電波として作り出す現象を、電磁波の相互変調とか、インターモジュレーション(IMD)と呼ぶ。

電源線路に重畳する電磁波も、対策をしないで放置すると、このような相互変調を繰り返して、沢山の新しい電磁波ノイズを生成する。

電源線路で起こるこのような電磁波の生成は、電磁 波をグランドへバイパスさせるキャパシタでは、全く対 策することができない。

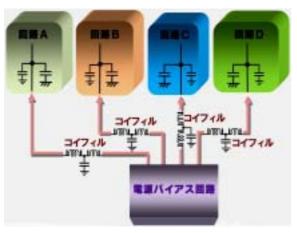

【図4】に示すように、個々の半導体集積回路に繋がる全ての電源線路を、インダクタによってフィルタリング(電磁波阻止)しない限り、このような相互変調をはじめとする電磁波ノイズの対策はできない。

# 9 RF プロック

PCBに搭載される高速動作半導体ごと、または動作機能毎に、「アイランド・セクション」すなわち、小さな領域にブロックされた電源線路網を構成して、そのひとつ一つの「島」と「島」を結ぶ電源線路には、GHz以上の周波数では高インピーダンスに見え、低い周波数では低抵抗の導体にしか見えない「コイフィル」を通して電源供給する。

【図4】 コイフィルを用いたRFブロック

このようなコイル・インダクタの採用は、今まで述べて きた「低インピーダンス化」電源線路設計者にとっては、 全く受け入れられない個別部品に見えるかもしれない。 従来の電磁波 /イズを発生させるインダクタ部品であると云われそうである。 けれども、この「コイフィル」は、 今までのコイル部品とは大きく違う。

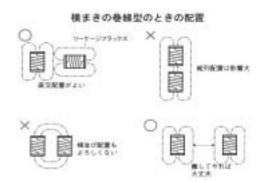

抵抗値が小さい。(数10m) 実装時の並列キャパシタンスが小さい。 ショート・リングを持つことで、従来のコイル 部品【図5】のような実装の配置制約がない。 0値を、制御することができる。

【図5】 従来のコイル部品配置制約[3]

### 10 まとめ

導体中の電磁波伝導を制御する事のできる受動素子部品は、抵抗とコイルしかないが、巻線コイルは電磁波を反射させて追い返す働きをする。

いままでコイル部品は、それほど重要視されてこなかったが、マイクロ波帯域の電磁波制御に無くてはならない部品である。

### 参考文献

- [1] NarimasaTakahasi, "A Terget Impedance Profit of Power Distribution Network" *JIEP Vol.12 No.3* (2009)

- [2] Osami Wada, "Fundamentals of PowerIntegrity Related to ChipsPackages and Printed Circuit Boards" *JIEP Vol.12 No.3* (2009)

- [3] 井上博文著: プリント板実装の高速・高周波対策 日刊工業新聞社

#### 連絡先

所属機関 ケイアールエフエム(株) 横浜技術 所在地 〒235-0033 横浜市磯子区杉田 2-12-8

電話番号 (045)772-4441 FAX番号 (045)772-5648 E-mail infor@krfm.co.jp